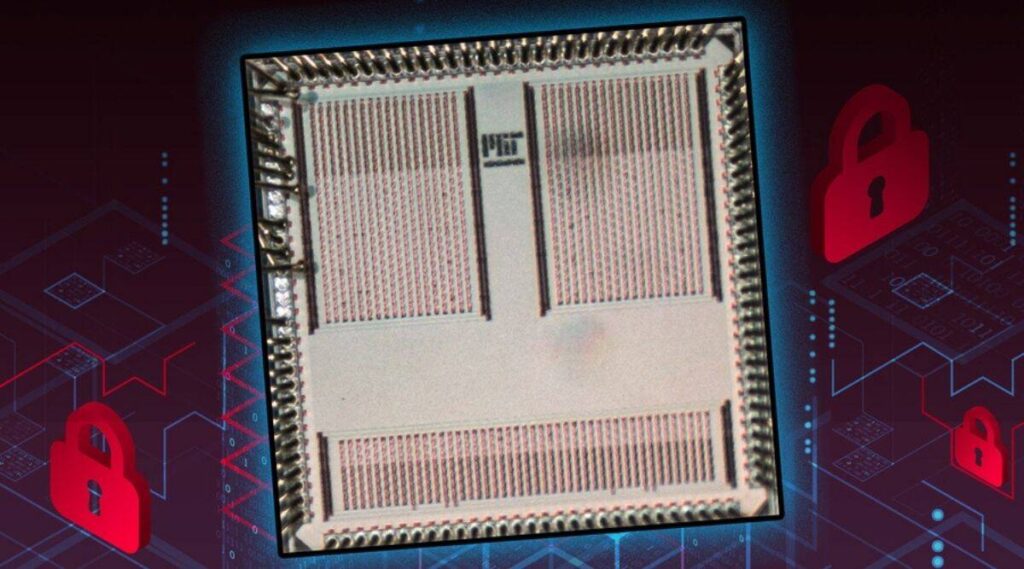

The researchers demonstrated the effectiveness of side-channel attacks on commercial microprocessors in an earlier paper before developing the new chip.

Written by Sethu Pradeep

Saurav Maji and Utsav Bannerjee, two Indian researchers working at the Massachusetts Institute of Technology (MIT), have built a low-energy security chip that is designed to prevent side-channel attacks (SCAs) on IoT (Internet of Things) devices. SCAs take advantage of security exploits where information can be gathered from the indirect effects of the functioning of the system hardware rather than attacking a programme or software directly.

“Traditionally, SCAs have been used in cryptography. If some data is being processed and there is a secret key used to encrypt or decrypt it, SCAs could be used in some cases to recover this key. It can be applied to any data that you want to keep secret. For example, it can be used on your smartwatch to extract your ECG and heart rate signal,” Maji, a graduate student at MIT and lead author of the paper, told indianexpress.com.

Side-channel attacks and their increasing viability

Typically, these attacks aim to extract sensitive information like cryptographic keys, proprietary machine learning models and parameters by measuring things like timing information, power consumption and electromagnetic leaks of a system.

In order to illustrate, let’s imagine that you want to find out whether your neighbour has been watering their garden. Using traditional attack methods, you would try to keep track of your neighbour to see if and when they are watering the plants in their garden.

But if you were to use the logic of an SCA, you would determine the same by measuring other auxiliary information like whether their plants are doing well, the amount of water they consume in the household, and whether they have the garden hose out. Here, you are using the information from the execution of an act to determine what is happening rather than looking at the act itself.

Even though SCAs are difficult to execute on most modern systems, the increasing sophistication of machine learning algorithms, greater computing power of devices and measuring devices with increasing sensitivities are making SCAs more of a reality.

Before developing the new security chip, Maji and Bannerjee, had published an attack paper titled “Leaky Nets: Recovering Embedded Neural Network Models and Inputs through Simple Power and Timing Side-Channels — Attacks and Defenses” in the IEEE Internet of Things Journal, under the guidance of Anantha Chandrakasan, the dean of the MIT School of Engineering and Vannevar Bush Professor of Electrical Engineering and Computer Science.

In the paper, they demonstrated the efficacy of SCAs by recovering machine learning model parameters and even inputs from the functioning of a commercial embedded microprocessor, similar to the ones used in commercial IoT devices.

How the new architecture could help

Since SCAs are difficult to detect and defend against, countermeasures against them have notoriously been very computing power and energy-intensive. This is where the new chip architecture comes in.

The MIT researchers presented their design in a paper titled “A Threshold-Implementation-Based Neural-Network Accelerator Securing Model Parameters and Inputs Against Power SCAs”, published in the International Solid State Circuits Conference 2022.

While Chandrakasan is the senior author of the paper, others who worked on it include. Banerjee, an MIT graduate and now assistant professor at the Indian Institute of Science, and Sam Fuller, a visiting research scientist at MIT.

The chip built by Maji and his collaborators is smaller than the size of a thumbnail and uses much less power than traditional security measures against SCAs. It has been built to be easily incorporated into smartwatches, tablets, and a variety of other devices.

“It can be used in any sensor nodes which connects user data. For example, it can be used in monitoring sensors in the oil and gas industry, it can be used in self-driving cars, in fingerprint matching devices and many other applications,” said Maji.

The chip uses near-threshold computing, a computing method where the data to be worked on is first split into separate, unique and random components. The chip then conducts operations separately on each component in a random order before aggregating the results for a final result.

Due to this method, the information leak from the device through power-consumption measurements are random and would reveal nothing but gibberish in an SCA. However, this method is energy and computation power-intensive while also requiring more system memory to store information.

Maji and others found a way to optimise this process to reduce some of the computational overheads. The researchers claim they have reduced the required computing overheads by three orders of magnitude with their chip architecture.

But at the same time, the implementation of this chip architecture in a system would require at least a five-fold increase in energy consumption 1.6 times the silicon area of an insecure implementation. Also, the architecture only protects against energy consumption-based SCAs and doesn’t defend against electromagnetic SCAs.

Source: indianexpress.com